# TGS32F103 Series MCU

Data sheet

## **Function**

- Core: ARM32-bit Cortex<sup>TM</sup>-M3 core

- Maximum operating frequency of 72MHz, up to 1.25DMips/MHz (Dhrystone2.1) when accessing the memory with 0 wait cycles

- Single cycle multiplication and hardware division

## Memory

- 64 KB or 128 KB program Flash

- 20 KB SRAM

## · Clock, reset and power management

- $-2.0 \sim 3.6 \text{ V}$  power supply and I/O pins

- Power-on/power-off reset (POR/PDR), programmable voltage monitor (PVD)

- 4 ~ 16 MHz crystal oscillator

- Embedded factory-tuned 8 MHz high-speed RC oscillator

- Built-in 40 kHz low-speed RC oscillator

- PLL that generates the CPU clock

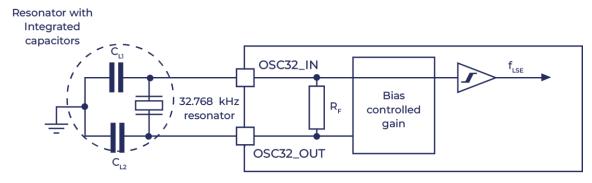

- 32 kHz RTC oscillator with calibration

#### Low power consumption

- Sleep, shutdown and standby modes

- $V_{\text{BAT}}$  powers the RTC and backup registers

# • 12-bit ADCs, 1ps conversion time (up to 16 inputs channel)

- Conversion range: 0 to 3.6 V

- Dual sampling and holding function

- Temperature sensor

#### • **DMA**:

- 7-channel DMA controller

- Supported peripherals: timers, ADC, SPI, I2C and USART

# • Up to 80 fast I/O ports

- 26/37/51/80 I/O ports on the O side, all I/O ports can be mapped to 16 external interrupts; almost all ports can withstand 5 V signals.

# • Debug mode

- Serial Single Wire Debug (SWD) and JTAG interface

#### • 7 timers

- 3 16-bit timers, each with up to 4 channels for input capture/output compare/PWM or pulse counting and incremental encoder inputs

- 16-bit PWM advanced control timer with dead zone control and emergency brake for motor control

- 2 watchdog timers (independent and windowed)

- System time timer: 24-bit self-decreasing counter

# • Up to 9 communication interfaces

- Up to 2 I2C interfaces (support SMBus/PMBus)

- Up to 3 USART interfaces (supports ISO7816 interface, LIN, IrDA interface and modem control)

- Up to 2 SPI interfaces (18Mbit/s)

- CAN interface (2.0B active)

- USB 2.0 full speed interface

## • CRC calculation unit, 96-bit unique chip identification code

#### 2. Description

The TGS32F103xB standard MCU series uses the high-performance ARM® Cortex<sup>TM</sup>-M3 32-bit RISC core, operating at 72 MHz, built-in high-speed memory (up to 128K bytes of flash memory and 20K bytes of SRAM), and rich enhanced I/O ports and peripherals connected to both APB buses. It contains 2 12-bit ADCs, 3 general-purpose 16-bit timers and 1 PWM timer. In addition, it also contains standard and advanced communication interfaces: up to 2 I2C interfaces and SPI interfaces, 3 USART interfaces, 1 USB interface and 1 CAN interface.

The TGS32F103xB standard MCU series products have a power supply voltage of 2.0 V to 3.6 V, an operating temperature range of -45°C to +105°C, and a series of power-saving modes to meet the requirements of low-power applications.

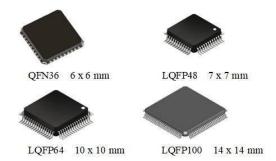

The TGS32F103xB standard series products provide 4 different package forms from 36 to 100 pins; depending on the package form, the peripheral configurations in the device are different. A basic introduction to all peripherals in this family of products is given below.

These rich peripheral configurations enable the TGS32F103xB standard series microcontrollers to be used in a variety of applications:

- Motor drives and application control

- Medical and handheld devices

- PC gaming peripherals and GPS platforms

- Industrial applications: Programmable controllers (PLCs), frequency converters, printers and scanners

- Alarm systems, video intercoms and HVAC systems, etc.

## 2.1 Device comparison

TGS32F103xB product functions and peripheral configuration

| Product model Peripheral interface |                                                                                                               | TGS32F103CB     | TGS32F103RB           | TGS32F103VB                             |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------------------------|

| - K Bytes                          | 128                                                                                                           | 128             | 128                   | 128                                     |

| Bytes                              | 20                                                                                                            | 20              | 20                    | 20                                      |

| Universal                          | 3                                                                                                             | 3               | 3                     | 3                                       |

| Advanced control                   | 1                                                                                                             | 1               | 1                     | 1                                       |

| SPI                                | 1                                                                                                             | 2               | 2                     | 2                                       |

| I2C                                | 1                                                                                                             | 2               | 2                     | 2                                       |

| USART                              | 2                                                                                                             | 3               | 3                     | 3                                       |

| USB                                | 1                                                                                                             | 1               | 1                     | 1                                       |

| CAN                                | 1                                                                                                             | 1               | 1                     | 1                                       |

| r of channels)                     | 26                                                                                                            | 37              | 51                    | 80                                      |

| ous ADC                            | 2                                                                                                             | 2               | 2                     | 2                                       |

| nannels)                           | 10 channels                                                                                                   | 10 channels     | 16 channels           | 16 channels                             |

| ency                               |                                                                                                               | 7               | 2 MHz                 |                                         |

| oltage                             |                                                                                                               | 2.0             | V ~3.6V               |                                         |

| perature                           |                                                                                                               | Ambient tempera | ature: -45°C ~ +105°C |                                         |

| tion                               | QFN36                                                                                                         | LQFP48          | LQFP64                | LQFP100                                 |

|                                    | - K Bytes Bytes Universal Advanced control SPI I2C USART USB CAN r of channels) tous ADC tannels) ency eltage | TGS32F103TB     | TGS32F103TB           | TGS32F103TB   TGS32F103CB   TGS32F103RB |

TRACECLK TRACED[0:3] TPIU POWER Trace/trig V<sub>DD</sub>=2 to 3.6V V<sub>ss</sub> SW/JTAG NJTRST VOLT. REG. JTDI JTCK/SWCLK JTMS/SWDIO JTDO ldo 3.3V TO 1.8V Flash 128 KB @VDD flash Cortex-M3 CPU F<sub>max</sub>:7 2M Hz NVIC @VDD OSC\_IN PCLK1 PCLK2 HCLK FCLK XTAL OSC 4-16MHz PLL& OSC\_OUT GP DMA CLOCK 7 channels RC 8 MHz IWDG @VDDA Stand by interface @VDDA SUPPLY SUPERVISION NRST VDDA VSSA @VBAT POR/PDR OSC32\_IN OSC32\_OUT XTAL 32 kHz AHB2 APB2 APB1 RTC Backup TAMPER-RTC EXTI WAKEUP 80AF Backup interface PA[15:0] **GPIOA** TIM2 PB[15:0] **GPIOB** TIM3 PC[15:0] **GPIOC** TIM4 PD[15:0] RX,TX,CTS,RTS USART2 PE[15:0] GPIOE RX,TX,CTS,RTS USART3 MOSI,MISO,SCK,NSS 4Channels 3 compl.Channels TIMI ETR and BKIN 12C1 SCL,SDA,SMBA as AF MOSI,MISO,SCK,NSS SPII 12C2 SCL,SDA as AF as AF RX,TX,CTS,RTS < USART1 bxCAN SmartCard as AF JUSBDP/CAN\_TX @VDDA USBDM/CAN\_RX 12bit ADC1 16AF VREF+ SRAM 512B 12bit ADC2 VREF-WWDG Temp sensor

Figure 1. Functional block diagram

- 1. Operating temperature: -45°C to +105°C, junction temperature up to 150°C.

- 2. AF: I/O port that can be used as a peripheral function pin

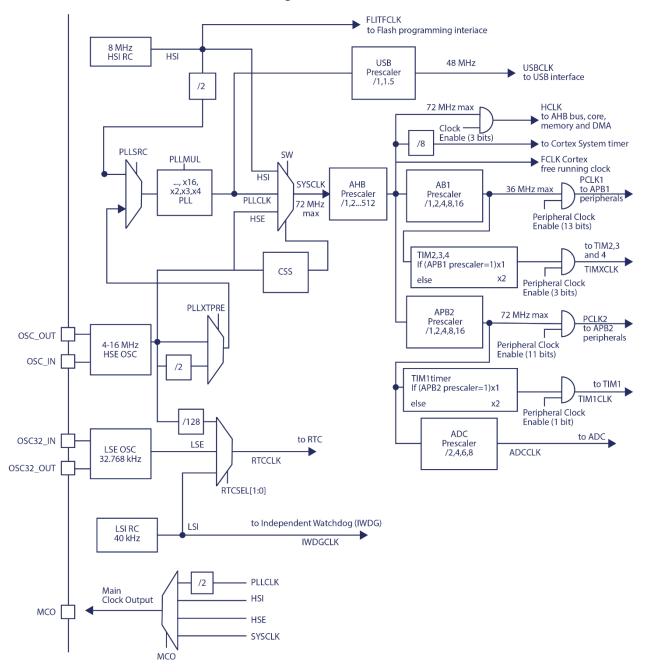

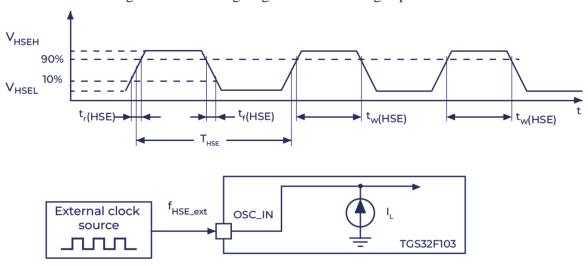

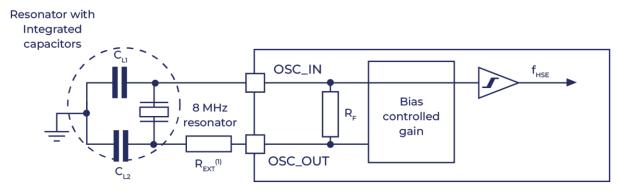

Figure 2. Clock tree

## Legend:

HSE = high-speed external clock signal

HSI = high-speed internal clock signal

LSI = low-speed internal clock signal

LSE = low-speed external clock signal

- $1. When \ HSI \ is \ used \ as \ the \ input \ of \ the \ PLL \ clock, \ the \ maximum \ system \ clock \ frequency \ can \ only \ reach \ 64MHz.$

- 2. When using the USB function, HSE and PLL must be used at the same time, and the CPU frequency must be  $48\,\mathrm{MHz}$  or  $72\,\mathrm{MHz}$ .

- 3. When the ADC sampling time is required to be 1µs, APB2 must be set at 14 MHz, 28 MHz or 56 MHz.

#### 2.2 Overview

# 2.2.1 ARM® Cortex<sup>TM</sup>-M3 core with embedded flash memory and SRAM

ARM's Cortex<sup>TM</sup>-M3 processor is the latest generation of embedded ARM processors. It provides a low-cost platform, reduced pin count and reduced system power consumption to implement MCU needs, while providing excellent computing performance and Advanced interrupt system response.

ARM's Cortex<sup>TM</sup>-M3 is a 32-bit RISC processor that provides additional code efficiency, leveraging the high performance of ARM cores on the memory space typically found in 8- and 16-bit systems.

The TGS32F103xB standard series has a built-in ARM core, making it compatible with all ARM tools and software. Figure 1 is the functional block diagram of this series of products.

# 2.2.2 Built-in flash memory

128K bytes of built-in flash memory for program and data.

#### 2.2.3 CRC (cyclic redundancy check) calculation unit

The CRC (Cyclic Redundancy Check) calculation unit uses a fixed polynomial generator to generate a CRC code from a 32-bit data word. In numerous applications, CRC-based techniques are used to verify the consistency of data transmission or storage. Within the scope of the EN/IEC 60335-1 standard, which provides a means of detecting flash memory errors, a CRC calculation unit can be used to calculate the signature of the software in real time and compare it with the signature generated when the software is linked and generated.

#### 2.2.4 Built-in SRAM

20K bytes of built-in SRAM, CPU can access (read/write) with 0 wait cycles.

#### 2.2.5 Nested Vectored Interrupt Controller (NVIC)

The TGS32F103xB standard product has a built-in nested vectored interrupt controller that can handle up to 43 maskable interrupt channels.

(Excluding 16 Cortex<sup>TM</sup>-M3 interrupt lines) and 16 priority levels.

- Tightly coupled NVIC enables low-latency interrupt response processing

- The interrupt vector entry address enters the kernel directly

- Tightly coupled NVIC interface

- Allow early handling of interrupts

- Handle late arriving higher priority interrupts

- Supports interrupt tail link function

- Automatically save processor state

- Automatic recovery on interrupt return without additional instruction overhead.

This module provides flexible interrupt management capabilities with minimal interrupt latency.

#### 2.2.6 External interrupt/event controller (EXTI)

The external interrupt/event controller contains 19 edge detectors for generating interrupt/event requests. Each interrupt line can independently configure its trigger event (rising edge or falling edge or both edges) and can be independently masked; a pending register maintains the status of all interrupt requests. EXTI can detect pulses whose width is less than the clock period of internal APB2. Up to 80 general-purpose I/O ports are connected to 16 external interrupt lines.

#### 2.2.7 Clock and startup

The system clock is selected at startup. The internal 8 MHz RC oscillator is selected as the default CPU clock at reset. Subsequently, an external 4 ~ 16 MHz clock with failure monitoring can be selected; when the external clock failure is detected, it will Isolated, the system will automatically switch to the internal RC oscillator, and if interrupts are enabled, the software can receive corresponding interrupts. Likewise, complete interrupt management of the PLL clock can be implemented when required (e.g., when the external oscillator used during a period fails).

Multiple prescalers are used to configure the AHB frequency, high-speed APB (APB2) and low-speed APB (APB1) regions. AHB and high speed the maximum frequency of APB is 72 MHz and the maximum frequency of low speed APB is 36MHz. Refer to the clock driver block diagram shown in Figure 2.

## 2.2.8 Bootstrap mode

- At startup, one of three bootstrap modes can be selected via the bootstrap pin:

- Boot from program flash memory

- Boot from system memory

- Boot from internal SRAM

The bootloader is stored in the system memory and the flash memory can be reprogrammed through USART1.

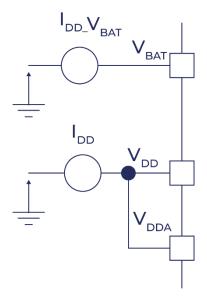

## 2.2.9 Power supply solution

- $V_{DD} = 2.0 \sim 3.6 \text{ V}$ : The  $V_{DD}$  pin supplies power to the I/O pins and internal voltage regulator.

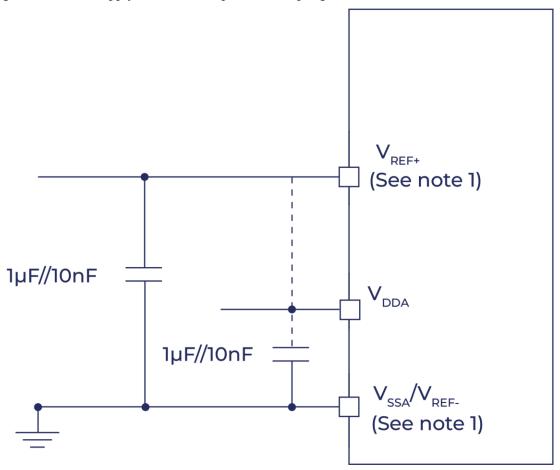

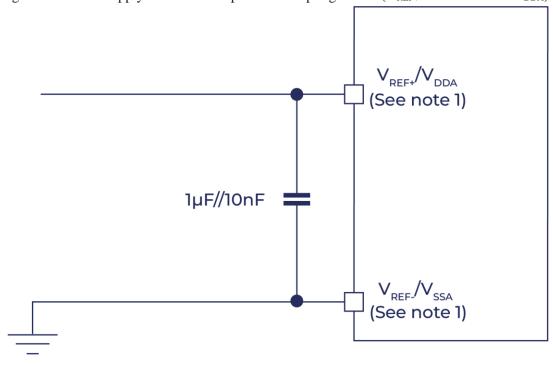

- $V_{SSA}$ ,  $V_{DDA}$ = 2.0 ~ 3.6 V: Provides power for the analog part of the ADC, reset module, RC oscillator and PLL. When using the ADC,  $V_{DDA}$  must not be less than 2.4 V.  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$  respectively.

- $V_{BAT} = 1.8 \sim 3.6 \text{ V}$ : When  $V_{DD}$  is turned off, power is supplied (via the internal power switch) to the RTC, external 32 kHz oscillator and backup registers.

See Figure 10 Power Supply Scheme for details on how to connect the power pins.

## 2.2.10 Power supply monitor

This product integrates a power-on reset (POR)/power-down reset (PDR) circuit. This circuit is always in working state to ensure that the system works when the power supply exceeds 2 V; when  $V_{DD}$  is lower than the set threshold ( $V_{POR/PDR}$ ), the device is placed in the reset state without using an external reset circuit. There is also a programmable voltage monitor (PVD) in the device, which monitors the  $V_{DD}$  / $V_{DDA}$  power supply and compares it with the threshold  $V_{PVD}$ . When  $V_{DD}$  is lower than or higher than the threshold  $V_{PVD}$ , an interrupt is generated. The interrupt handler can issue a warning message or set the microcontroller goes into safe mode. The PVD function needs to be enabled through a program. Refer to Table 8 for  $V_{POR/PDR}$  and  $V_{PVD}$  values.

#### 2.2.11 Voltage regulator

The voltage regulator has three operating modes: main mode (MR), low power mode (LPR) and shutdown mode

- Master mode (MR) for normal running operation

- Low power mode (LPR) for CPU shutdown mode

- Shutdown mode is used in the standby mode of the CPU: the output of the voltage regulator is in a high-impedance state, the power supply to the core circuit is cut off, and the voltage regulator is in a

zero-consumption state (but the contents of the register and SRAM will be lost)

The regulator is always active after reset and shuts down in standby mode with a high-impedance output.

#### 2.2.12 Low power mode

The TGS32F103xB standard product supports three low-power modes to achieve the best balance between low power consumption, short startup time and multiple wake-up events.

#### Sleep mode

In sleep mode, only the MCU is stopped, all peripherals are active and can wake up the MCU when an interrupt/event occurs.

#### Shutdown mode

Stop mode can achieve the lowest power consumption without losing SRAM and register contents. In shutdown mode, the power supply to all internal 1.5 V parts is stopped, the PLL, HSI's RC oscillator and HSE crystal oscillator are turned off, and the voltage regulator can be placed in normal mode or low power mode.

The microcontroller can be woken up from Stop mode by any signal configured as EXTI. The EXTI signal can be 16 external one of the I/O ports, PVD output, RTC alarm clock or USB wake-up signal.

## Standby mode

The lowest power consumption can be achieved in standby mode. The internal voltage regulator is turned off, so the power supply to all internal 1.5 V parts is cut off; the PLL, HSI RC oscillator and HSE crystal oscillator are also turned off; after entering standby mode, the contents of SRAM and registers will disappear, but the contents of the backup register are still retained and the standby circuit is still working.

The conditions for exiting from standby mode are: an external reset signal on NRST, an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm.

Note: When entering shutdown or standby mode, RTC, IWDG and their corresponding clocks will not be stopped.

#### 2.2.13 DMA

Flexible 7-way general-purpose DMA manages memory-to-memory, device-to-memory, and memory-to-device data transfers;

The DMA controller supports ring buffer management, which avoids interrupts when the controller transfer reaches the end of the buffer.

Each channel has dedicated hardware DMA request logic, and each channel can be triggered by software; the length of the transfer, the source address and destination address of the transfer can be set individually through software.

DMA can be used with the main peripherals: SPI, I2C, USART as well as general-purpose, high-level control timers TIMx and ADC.

#### 2.2.14 RTC (real-time clock) and backup register

The RTC and backup registers are powered through a switch that selects VDD when VDD is valid, otherwise powered by the VBAT pin. The backup registers (10 16-bit registers) can be used to save 20 bytes of user application data when VDD is turned off. The RTC and backup registers are not reset by system or power reset sources, nor are they reset when waking from standby mode.

The real-time clock has a set of continuously running counters, can provide a calendar clock function

through appropriate software, and also has alarm interrupt and stage interrupt functions. The driving clock of the RTC can be a 32.768kHz oscillator using an external crystal, an internal low-power RC oscillator, or a high-speed external clock divided by 128. The internal low-power RC oscillator has a typical frequency of 40kHz. To compensate for natural crystal deviations, the RTC's clock can be calibrated by outputting a 512Hz signal. The RTC has a 32-bit programmable counter that allows long-term measurements using the compare register. There is a 20-bit prescaler for the time base clock which will produce a one second long time base by default when the clock is 32.768kHz.

#### 2.2.15 Timers and watchdogs

The TGS32F103xB standard series includes 1 advanced control timer, 3 general-purpose timers, 2 watchdog timers and 1 system timer.

The following table compares the functionality of advanced control timers, normal timers, and basic timers:

| Timer                | Counter resolution | Counter type        | Prescaler<br>coefficient                 | Generate DMA<br>request | Capture/compare channels | Compleme<br>ntary<br>output |

|----------------------|--------------------|---------------------|------------------------------------------|-------------------------|--------------------------|-----------------------------|

| TIM1                 | 16 bit             | Count up/down count | Any number<br>between 1~65536<br>integer | Can                     | 4                        | Have                        |

| TIM2<br>TIM3<br>TIM4 | 16 bit             | Count up/count down | Any integer between 1~65536              | Can                     | 4                        | No                          |

Table 1. Timer function comparison

## Advanced control timer (TIM1)

The Advanced Control Timer (TIM1) can be viewed as a three-phase PWM generator assigned to 6 channels, with complementary PWM outputs with dead-band insertion, or as a complete general-purpose timer. 4 independent channels can be used for:

- Input capture

- Output comparison

- Generate PWM (edge or center aligned mode)

- Single pulse output

When configured as a 16-bit standard timer, it has the same functionality as the TIMx timer. When configured as a 16-bit PWM generator, it has full modulation capability (0~100%).

In debug mode, the counters can be frozen and the PWM outputs disabled, thereby turning off the switches controlled by these outputs. Many functions are the same as the standard TIM timer and the internal structure is the same, so the advanced control timer can operate in conjunction with the TIM timer through the timer link function to provide synchronization or event link functions.

#### **General purpose timer (TIMx)**

The TGS32F103xB standard product has built-in up to 3 standard timers (TIM2, TIM3 and TIM4) that can run synchronously. Each timer has a 16-bit auto-loading up/down counter, a 16-bit prescaler and 4 independent channels, each channel can be used for input capture, output compare, PWM and single pulse mode Outputs, providing up to 12 input capture, output compare, or PWM channels in the largest package configuration.

They can also work with advanced control timers via the timer linking feature, providing synchronization or event linking capabilities. In debug mode, the counter can be frozen. Any standard timer can be used to generate the PWM output. Each timer has an independent DMA

request mechanism.

These timers are also capable of processing the signals of incremental encoders, as well as the digital outputs of 1 to 3 Hall sensors.

#### **Independent watchdog**

The independent watchdog is based on a 12-bit down counter and an 8-bit prescaler, which is clocked by an internal independent 40 kHz RC oscillator; because this RC oscillator is independent of the main clock, it can run in shutdown mode and standby mode. It can be used as a watchdog to reset the entire system when a problem occurs, or as a free timer to provide timeout management for applications. The watchdog can be configured to be software or hardware enabled through the option byte. In debug mode, counters can be frozen.

## Window watchdog

The window watchdog contains a 7-bit down counter that can be configured as a free-running counter. When used as a watchdog, the entire system can be reset if a problem occurs. It is driven by the main clock and has an early warning interrupt function; in debug mode, the counter can be frozen.

#### System time base timer

This timer can be used exclusively in real-time operating systems, or it can be used as a standard down counter. It has the following characteristics:

- 24-bit down counter

- · Auto-reload feature

- Can generate a maskable system interrupt when the counter reaches 0

- Programmable clock source

#### 2.2.16 I2C bus

Up to 2 I2C bus interfaces, capable of working in multi-master mode or slave mode, supporting standard mode and fast mode.

The I2C interface supports 7-bit or 10-bit addressing, and the 7-bit slave mode supports dual slave address addressing. Built-in hardware CRC generator/checker. The interface operates using DMA and supports the SMBus bus version 2.0/PMBus bus.

#### 2.2.17 Universal Synchronous/Asynchronous Receiver-Transmitter (USART)

The communication rate of the USART1 interface can reach 4.5 Mb/s, and the communication rate of other interfaces can reach 2.25 Mb/s. The USART interface has hardware CTS and RTS signal management, supports IrDA SIR ENDEC transmission codec, is compatible with ISO7816 smart cards and provides LIN master/slave functionality. All USART interfaces can use DMA operations.

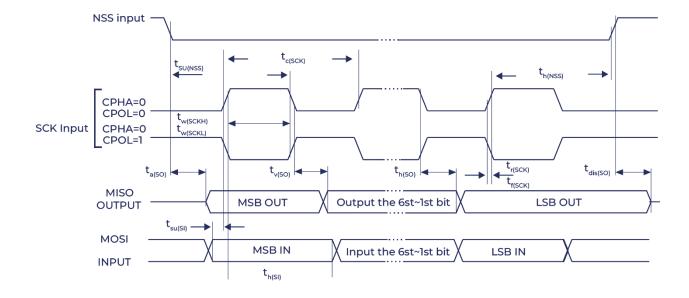

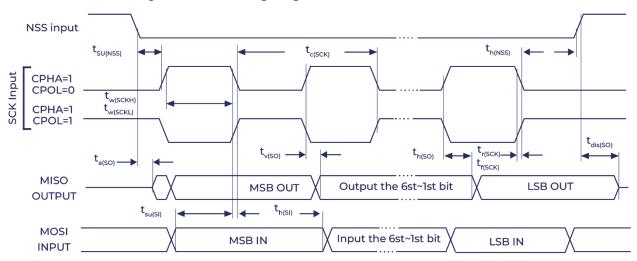

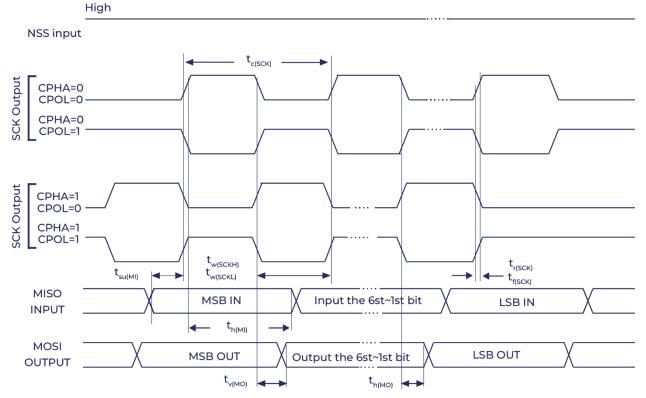

# 2.2.18 Serial Peripheral Interface (SPI)

Up to 2 SPI interfaces, configurable in slave or master mode, with communication rates up to 18 Mb/s in full and half duplex. The 3-bit prescaler generates 8 master mode frequencies, configurable into 8-bit or 16-bit data frame format. Hardware CRC generation/checking supports basic SD card and MMC modes.

All SPI interfaces can use DMA operations.

#### 2.2.19 Controller Area Network (CAN)

The CAN interface is compatible with specifications 2.0A and 2.0B (active) with bit rates up to 1 Mb/s. It can receive and send standard frames with an 11-bit identifier, or extended frames with a 29-

bit identifier. Features 3 send mailboxes and 2 receive FIFOs, 3 levels of 14 adjustable filters.

## 2.2.20 Universal Serial Bus (USB)

The TGS32F103xB standard series products embed a device controller compatible with full-speed USB and comply with the full-speed USB device (12 Mb/s) standard, endpoints are software configurable with standby/wake capabilities. The USB-specific 48 MHz clock is generated directly by the internal main PLL (the clock source must be an HSE crystal oscillator).

## 2.2.21 General input and output interface (GPIO)

Each GPIO pin can be configured by software as an output (push-pull or open-drain), input (pull-up or pull-down or floating), or a multiplexed peripheral function port. Most GPIO pins are shared with multiplexed digital or analog peripherals. In addition to having analog input capabilities, all GPIO pins allow large currents to pass through them.

If desired, the peripheral function of an I/O pin can be locked by a specific operation to avoid accidental writes to the I/O registers. The I/O pins on APB2 can toggle up to 18 MHz.

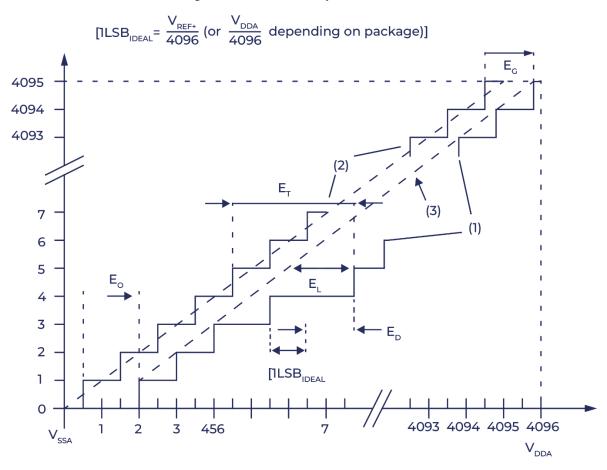

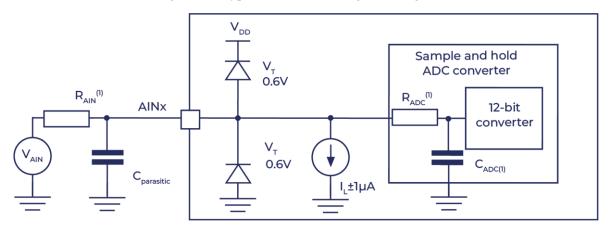

# 2.2.22 ADC (analog/digital converter)

The TGS32F103xB standard product embeds two 12-bit analog/digital converters (ADCs). Each ADC shares up to 16 external channels and can achieve single conversion or scan mode conversion. In scan mode, conversions are automatically performed on a selected set of analog input pins.

Other logic functions on the ADC interface include:

- Synchronized sample and hold

- Interleaved sample and hold

- Single sampling

The ADC can operate using DMA.

The analog watchdog can monitor one, multiple or all selected channels very accurately. When the monitored signal exceeds the preset threshold, the analog watchdog will generate an interrupt.

Events generated by the standard timer (TIMx) and the advanced control timer (TIM1) can be internally cascaded to the start trigger and injection trigger of the ADC respectively, and the application can synchronize the AD conversion with the clock.

# 2.2.23 Temperature sensor

The temperature sensor generates a voltage that changes linearly with temperature, with a conversion range of 2 V < VDDA < 3.6 V. The temperature sensor is internally connected to the input channel of ADC1 IN16, which converts the sensor output to a digital value.

## 2.2.24 Serial single-wire JTAG debug port (SWJ-DP)

Embedded ARM's SWJ-DP interface, which is an interface that combines JTAG and serial single-wire debugging, can realize the connection of the serial single-wire debugging interface or the JTAG interface. The TMS and TCK signals of JTAG share pins with SWDIO and SWCLK respectively. A special signal sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

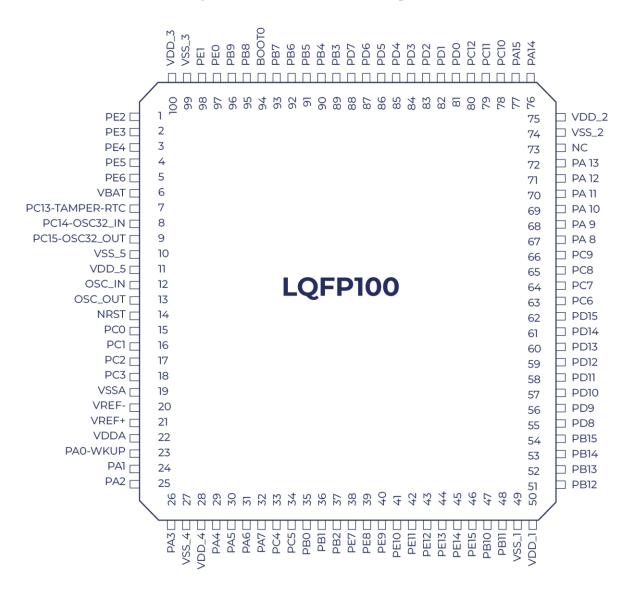

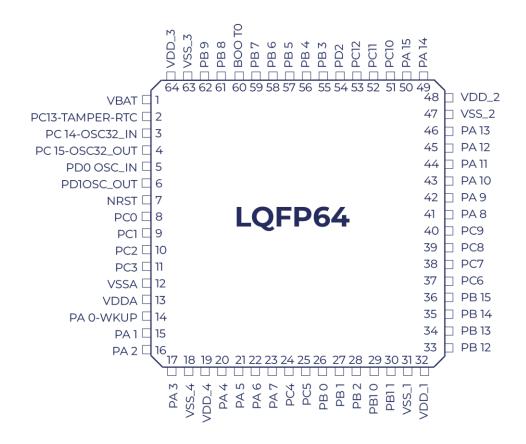

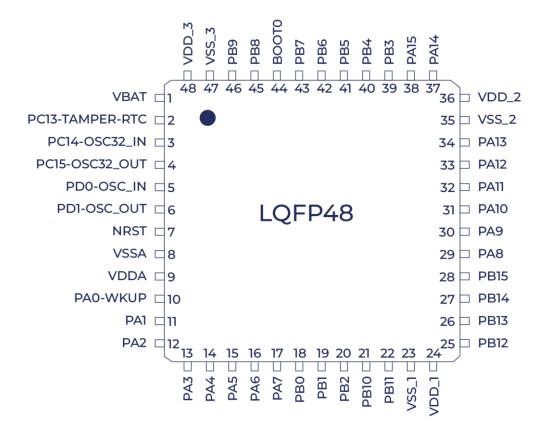

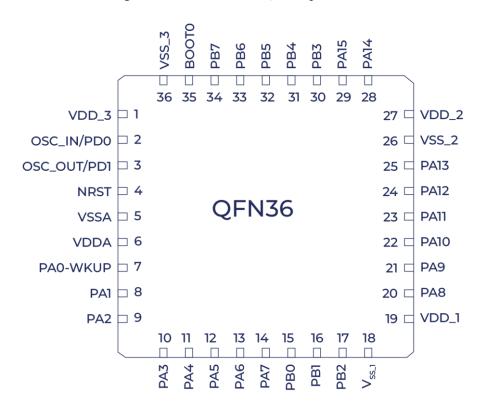

## 3. Pin definition

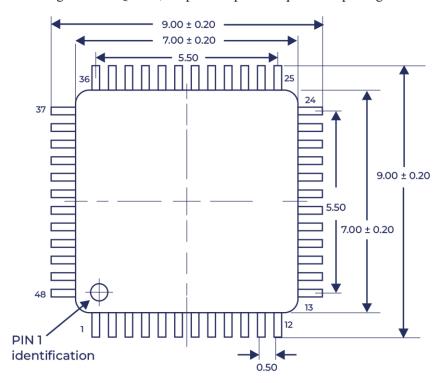

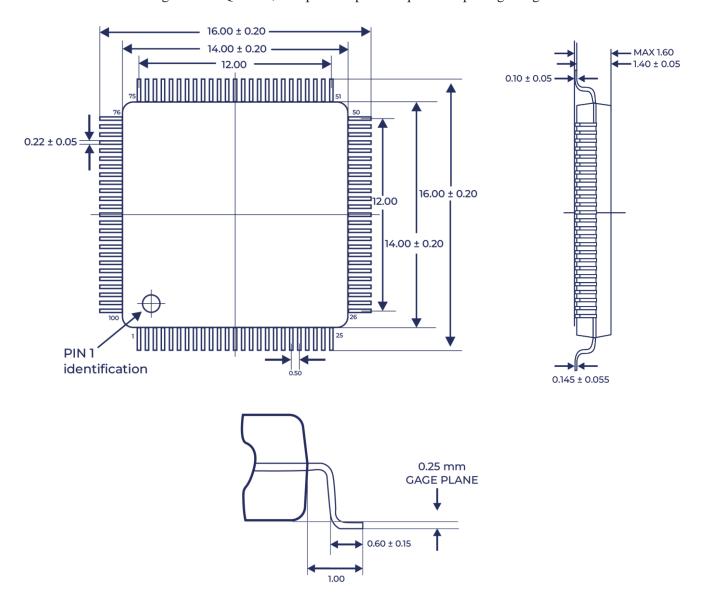

Figure 3. TGS32F103xB LQFP100 pin distribution

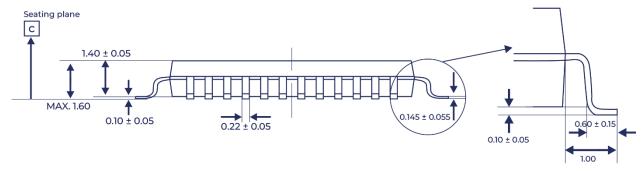

Figure 4. TGS32F103xB LQFP64 pin distribution

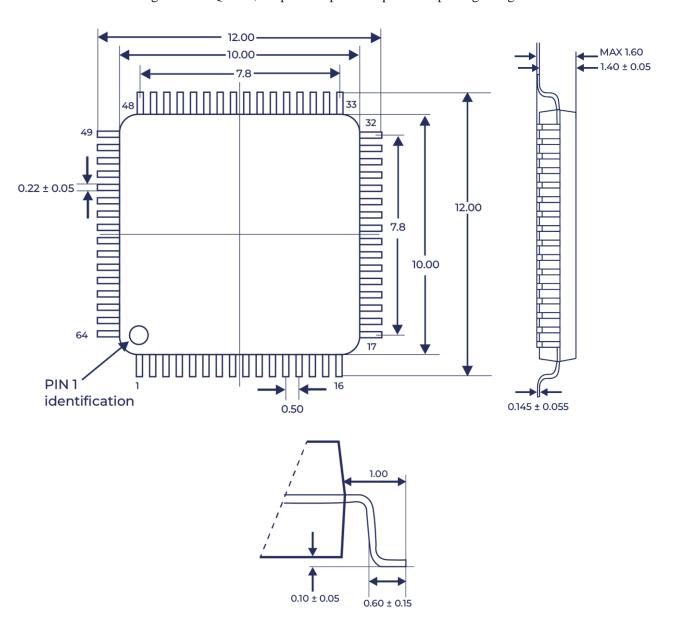

Figure 5. TGS32F103xB LQFP48 pin distribution

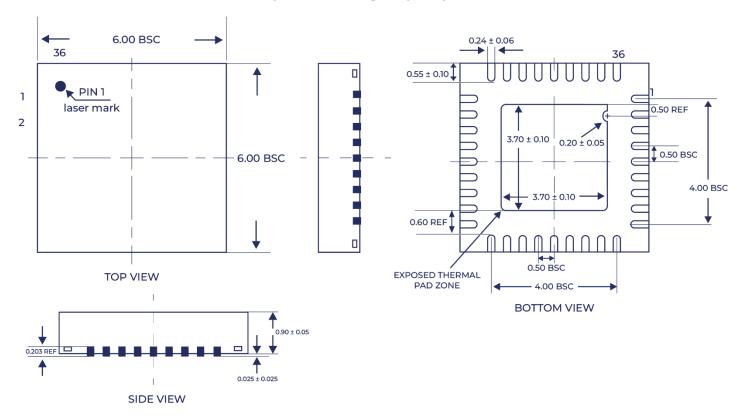

Figure 6. TGS32F103xB QFN36 pin distribution

Table 2. TGS32F103XBxx pins definition

| Fo     | ot posi | tion    |        |                        |                  | 5)                      |                              | Ontional ro            | euse function     |

|--------|---------|---------|--------|------------------------|------------------|-------------------------|------------------------------|------------------------|-------------------|

| 48     | 64      | 100     | 36     | 75.1                   | e <sup>(1)</sup> | vel <sup>C</sup>        | Main function <sup>(3)</sup> | Optional re            | cuse function     |

| LQFP48 | LQFP64  | LQFP100 | QFPN36 | Pin name               | $Type^{(1)}$     | IO level <sup>(2)</sup> | (after reset)                | Default reuse function | Redefine function |

| -      | -       | 1       | -      | PE2                    | I/O              | FT                      | PE2                          | TRACECK                |                   |

| -      | -       | 2       | -      | PE3                    | I/O              | FT                      | PE3                          | TRACED0                |                   |

| -      | -       | 3       | -      | PE4                    | I/O              | FT                      | PE4                          | TRACED1                |                   |

| -      | -       | 4       | -      | PE5                    | I/O              | FT                      | PE5                          | TRACED2                |                   |

| -      | -       | 5       | -      | PE6                    | I/O              | FT                      | PE6                          | TRACED3                |                   |

| 1      | 1       | 6       | -      | VBAT                   | S                |                         | VBAT                         |                        |                   |

| 2      | 2       | 7       | -      | PC13-<br>TAMPER- RTC   | I/O              |                         | PC13                         | TAMPER-RTC             |                   |

| 3      | 3       | 8       | -      | PC14- OSC32_IN         | I/O              |                         | PC14                         | OSC32_IN               |                   |

| 4      | 4       | 9       | _      | PC15-<br>OSC32_OUT (5) | I/O              |                         | PC15                         | OSC32_OUT              |                   |

| -      | -       | 10      | -      | VSS_5                  | S                |                         | VSS_5                        |                        |                   |

| -      | -       | 11      | -      | VDD_5                  | S                |                         | VDD_5                        |                        |                   |

| 5      | 5       | 12      | 2      | OSC_IN                 | I                |                         | OSC_IN                       |                        | PD0(7)            |

| 6      | 6       | 13      | 3      | OSC_OUT                | О                |                         | OSC_OUT                      |                        | PD1(7)            |

| 7      | 7       | 14      | 4      | NRST                   | I/O              |                         | NRST                         |                        |                   |

| -      | 8       | 15      | -      | PC0                    | I/O              |                         | PC0                          | ADC12_IN10             |                   |

| -      | 9       | 16      | -      | PC1                    | I/O              |                         | PC1                          | ADC12_IN11             |                   |

| -      | 10      | 17      | -      | PC2                    | I/O              |                         | PC2                          | ADC12_IN12             |                   |

| -      | 11      | 18      | -      | PC3                    | I/O              |                         | PC3                          | ADC12_IN13             |                   |

| 8      | 12      | 19      | 5      | VSSA                   | S                |                         | VSSA                         |                        |                   |

| -      | -       | 20      | -      | VREF-                  | S                |                         | VREF-                        |                        |                   |

| -      | -       | 21      | -      | VREF+                  | S                |                         | VREF+                        |                        |                   |

| 9      | 13      | 22      | 6      | VDDA                   | S                |                         | VDDA                         |                        |                   |

| 10 | 14 | 23 | 7  | PA0-WKUP | I/O | PA0   | WKUP/USART2_CT<br>S<br>/ADC12_IN0/TIM2_<br>CH1_ETR |           |

|----|----|----|----|----------|-----|-------|----------------------------------------------------|-----------|

| 11 | 15 | 24 | 8  | PA1      | I/O | PA1   | USART2_RTS<br>/ADC12_IN1/TIM2_<br>CH2              |           |

| 12 | 16 | 25 | 9  | PA2      | I/O | PA2   | USART2_TX<br>/ADC12_IN2/TIM2_<br>CH3               |           |

| 13 | 17 | 26 | 10 | PA3      | I/O | PA3   | USART2_RX<br>/ADC12_IN3/TIM2_<br>CH4               |           |

| -  | 18 | 27 | -  | VSS_4    | S   | VSS_4 |                                                    |           |

| -  | 19 | 28 | -  | VDD_4    | S   | VDD_4 |                                                    |           |

| 14 | 20 | 29 | 11 | PA4      | I/O | PA4   | SPI1_NSS<br>/USART2_CK<br>/ADC12_IN4               |           |

| 15 | 21 | 30 | 12 | PA5      | I/O | PA5   | SPI1_SCK<br>/ADC12_IN5                             |           |

| 16 | 22 | 31 | 13 | PA6      | I/O | PA6   | SPI1_MISO<br>/ADC12_IN6/TIM3_<br>CH1               | TIM1_BKIN |

| 17 | 23 | 32 | 14 | PA7      | I/O | PA7   | SPI1_MOSI<br>/ADC12_IN7/TIM3_<br>CH2               | TIM1_CH1N |

| -  | 24 | 33 |    | PC4      | I/O | PC4   | ADC12_IN14                                         |           |

| -  | 25 | 34 |    | PC5      | I/O | PC5   | ADC12_IN15                                         |           |

| 18 | 26 | 35 | 15 | PB0      | I/O | PB0   | ADC12_IN8/TIM3_C<br>H3                             | TIM1_CH2N |

|          | Foot p | osition |        |             |                     | 2)                      |                              | Optional reuse                                  | function          |

|----------|--------|---------|--------|-------------|---------------------|-------------------------|------------------------------|-------------------------------------------------|-------------------|

| <b>∞</b> | 64     | 00      | 36     |             | e <sup>(1)</sup>    | /el                     | Main function <sup>(3)</sup> | Optional reuse                                  | Tunction          |

| LQFP48   | LQFP64 | LQFP100 | QFPN36 | Pin name    | Type <sup>(1)</sup> | IO level <sup>(2)</sup> | (after reset)                | <b>Default reuse function</b>                   | Redefine function |

| 19       | 27     | 36      | 16     | PB1         | I/O                 |                         | PB1                          | ADC12_IN9/TIM3_CH4                              | TIM1_CH3N         |

| 20       | 28     | 37      | 17     | PB2         | I/O                 | FT                      | PB2/BOOT1                    |                                                 |                   |

| -        | -      | 38      | -      | PE7         | I/O                 | FT                      | PE7                          |                                                 | TIM1_ETR          |

| -        | -      | 39      | -      | PE8         | I/O                 | FT                      | PE8                          |                                                 | TIM1_CH1N         |

| -        | -      | 40      | -      | PE9         | I/O                 | FT                      | PE9                          |                                                 | TIM1_CH1          |

| -        | -      | 41      | -      | PE10        | I/O                 | FT                      | PE10                         |                                                 | TIM1_CH2N         |

| -        | -      | 42      | -      | PE11        | I/O                 | FT                      | PE11                         |                                                 | TIM1_CH2          |

| -        | -      | 43      | -      | PE12        | I/O                 | FT                      | PE12                         |                                                 | TIM1_CH3N         |

| -        | -      | 44      | -      | PE13        | I/O                 | FT                      | PE13                         |                                                 | TIM1_CH3          |

| -        | -      | 45      | -      | PE14        | I/O                 | FT                      | PE14                         |                                                 | TIM1_CH4          |

| -        | -      | 46      | -      | PE15        | I/O                 | FT                      | PE15                         |                                                 | TIM1_BKIN         |

| 21       | 29     | 47      | 1      | PB10        | I/O                 | FT                      | PB10                         | I2C2_SCL/USART3_<br>TX                          | TIM2_CH3          |

| 22       | 30     | 48      | -      | PB11        | I/O                 | FT                      | PB11                         | I2C2_SDA/USART3_RX                              | TIM2_CH4          |

| 23       | 31     | 49      | 18     | $V_{SS\_1}$ | S                   |                         | $ m V_{SS\_1}$               |                                                 |                   |

| 24       | 32     | 50      | 19     | $V_{DD}_1$  | S                   |                         | $V_{\mathrm{DD}}$ 1          |                                                 |                   |

| 25       | 33     | 51      | ı      | PB12        | I/O                 | FT                      | PB12                         | SPI2_NSS/I2C2_SM<br>BAI/USART3_CK<br>/TIM1_BKIN |                   |

| 26       | 34     | 52      | 1      | PB13        | I/O                 | FT                      | PB13                         | SPI2_SCK/USART3_<br>CTS /TIM1_CH1N              |                   |

| 27       | 35     | 53      | -      | PB14        | I/O                 | FT                      | PB14                         | SPI2_MISO/USART3<br>_RTS TIM1_CH2N              |                   |

| 28 | 36 | 54 | _  | PB15               | I/O | FT | PB15               | CDI2 MOCL/TIM1 CH2N                    |                                |

|----|----|----|----|--------------------|-----|----|--------------------|----------------------------------------|--------------------------------|

| 28 | 30 | 54 | -  | PB15               | 1/0 | гі | PB15               | SPI2_MOSI/TIM1_CH3N                    |                                |

| -  | -  | 55 | -  | PD8                | I/O | FT | PD8                |                                        | USART3_TX                      |

| -  | -  | 56 | -  | PD9                | I/O | FT | PD9                |                                        | USART3_RX                      |

| -  | -  | 57 | -  | PD10               | I/O | FT | PD10               |                                        | USART3_CK                      |

| -  | -  | 58 | -  | PD11               | I/O | FT | PD11               |                                        | USART3_CTS                     |

| -  | 1  | 59 | -  | PD12               | I/O | FT | PD12               |                                        | TIM4_CH1<br>/USART3_RTS        |

| -  | -  | 60 | -  | PD13               | I/O | FT | PD13               |                                        | TIM4_CH2                       |

| -  | -  | 61 | -  | PD14               | I/O | FT | PD14               |                                        | TIM4_CH3                       |

| -  | -  | 62 | -  | PD15               | I/O | FT | PD15               |                                        | TIM4_CH4                       |

| -  | 37 | 63 | -  | PC6                | I/O | FT | PC6                |                                        | TIM3_CH1                       |

|    | 38 | 64 | -  | PC7                | I/O | FT | PC7                |                                        | TIM3_CH2                       |

|    | 39 | 65 | -  | PC8                | I/O | FT | PC8                |                                        | TIM3_CH3                       |

| -  | 40 | 66 | -  | PC9                | I/O | FT | PC9                |                                        | TIM3_CH4                       |

| 29 | 41 | 67 | 20 | PA8                | I/O | FT | PA8                | USART1_CK/TIM1_CH1<br>/MCO             |                                |

| 30 | 42 | 68 | 21 | PA9                | I/O | FT | PA9                | USART1_TX<br>/TIM1_CH2                 |                                |

| 31 | 43 | 69 | 22 | PA10               | I/O | FT | PA10               | USART1_RX<br>/TIM1_CH3                 |                                |

| 32 | 44 | 70 | 23 | PA11               | I/O | FT | PA11               | USART1_CTS/CANRX<br>/USBDM/TIM1_CH4    |                                |

| 33 | 45 | 71 | 24 | PA12               | I/O | FT | PA12               | USART1_RTS/<br>CANTX/USBDPTIM<br>1_ETR |                                |

| 34 | 46 | 72 | 25 | PA13               | I/O | FT | JTMS/SWDIO         | _                                      | PA13                           |

| -  | -  | 73 | -  |                    |     |    | Not connec         | ted                                    |                                |

| 35 | 47 | 74 | 26 | $V_{SS_2}$         | S   |    | $ m V_{SS\_2}$     |                                        |                                |

| 36 | 48 | 75 | 27 | V <sub>DD</sub> _2 | S   |    | V <sub>DD</sub> _2 |                                        |                                |

| 37 | 49 | 76 | 28 | PA14               | I/O | FT | JTCK/SWCLK         |                                        | PA14                           |

| 38 | 50 | 77 | 29 | PA15               | I/O | FT | JTDI               |                                        | TIM2_CH1_ETR/<br>PA15/SPI1_NSS |

|        | Foot p | ositior |        |          |         |             |                  |                           |                                      |

|--------|--------|---------|--------|----------|---------|-------------|------------------|---------------------------|--------------------------------------|

|        |        |         |        |          | Œ       | el(2        | Main function(3) | Optional re               | euse function                        |

| LQFP48 | LQFP64 | LQFP100 | QFPN36 | Pin name | Type(1) | IO level(2) | (after reset)    | Default reuse<br>function | Redefine function                    |

| -      | 51     | 78      |        | PC10     | I/O     | FT          | PC10             |                           | USART3_TX                            |

| -      | 52     | 79      |        | PC11     | I/O     | FT          | PC11             |                           | USART3_RX                            |

| -      | 53     | 80      |        | PC12     | I/O     | FT          | PC12             |                           | USART3_CK                            |

| -      | -      | 81      | 2      | PD0      | I/O     | FT          | PD0              |                           | CANRX                                |

| -      | -      | 82      | 3      | PD1      | I/O     | FT          | PD1              |                           | CANTX                                |

|        | 54     | 83      | -      | PD2      | I/O     | FT          | PD2              | TIM3_ETR                  |                                      |

| -      | -      | 84      | -      | PD3      | I/O     | FT          | PD3              |                           | USART2_CTS                           |

| -      | -      | 85      | -      | PD4      | I/O     | FT          | PD4              |                           | USART2_RTS                           |

| -      | -      | 86      | -      | PD5      | I/O     | FT          | PD5              |                           | USART2_TX                            |

| -      | -      | 87      | -      | PD6      | I/O     | FT          | PD6              |                           | USART2_RX                            |

| -      | -      | 88      | -      | PD7      | I/O     | FT          | PD7              |                           | USART2_CK                            |

| 39     | 55     | 89      | 30     | PB3      | I/O     | FT          | JTDO             |                           | TIM2_CH2<br>/PB3TRACESWOSP<br>I1_SCK |

| 40     | 56     | 90      | 31     | PB4      | I/O     | FT          | JNTRST           |                           | TIM3_CH1/PB4/SPI<br>1_MISO           |

| 41     | 57     | 91      | 32     | PB5      | I/O     |             | PB5              | I2C1_SMBAl                | TIM3_CH2<br>/SPI1_MOSI               |

| 42     | 58     | 92      | 33     | PB6      | I/O     | FT          | PB6              | I2C1_SCL<br>/TIM4_CH1     | USART1_TX                            |

| 43     | 59     | 93      | 34     | PB7      | I/O     | FT          | PB7              | I2C1_SDA<br>/TIM4_CH2     | USART1_RX                            |

| 44     | 60     | 94      | 35     | BOOT0    | I       |             | BOOT0            |                           |                                      |

| 45     | 61     | 95      | -      | PB8      | I/O     | FT          | PB8              | TIM4_CH3                  | I2C1_SCL /CANRX                      |

| 46     | 62     | 96      | -      | PB9      | I/O     | FT          | PB9              | TIM4_CH4                  | I2C1_SDA/CANTX                       |

| -      | -      | 97      | -      | PE0      | I/O     | FT          | PE0              | TIM4_ETR                  |                                      |

| -  | -  | 98  | -  | PE1               | I/O | FT | PE1               |  |

|----|----|-----|----|-------------------|-----|----|-------------------|--|

| 47 | 63 | 99  | 36 | $V_{SS_3}$        | S   |    | $V_{SS\_3}$       |  |

| 48 | 64 | 100 | 1  | V <sub>DD</sub> 3 | S   |    | V <sub>DD</sub> 3 |  |

- 1. I = input, O = output, S = power supply

- 2. FT: 5 V voltage tolerance

- 3. PC13, PC14 and PC15 pins are powered by the power switch, and this power switch can only sink limited current (3 mA). Therefore, these three pins have the following limitations when used as output pins: only one pin can be used as an output at the same time. When used as an output pin, it can only work in 2 MHz mode, the maximum driving load is 30 pF, and it cannot be used as a current source (Such as driving LED).

- 4. These pins are in the main function state when the backup area is powered on for the first time. Even if reset later, the status of these pins is controlled by the backup area registers (these registers will not be reset by the main reset system). For specific information on how to control these IO ports, please refer to the relevant chapters of the battery backup area and BKP register in the TGS32F103xB reference manual.

- 5. This type of alternate function can be configured by software to other pins (if the corresponding package model has this pin). For details, please refer to the alternate function I/O chapter and debugging settings chapter of the TGS32F103xB reference manual.

- 6. Pins 2 and 3 of the QFN36 package, and pins 5 and 6 of the LQFP48 and LQFP64 packages are configured as OSC\_IN and OSC\_OUT function pins by default after the chip is reset. Software can reset these two pins to the PD0 and PD1 functions. But for the LQFP100 package, since PD0 and PD1 are inherent function pins, there is no need to reimage settings by software. For more details, please refer to the Alternate Function I/O Chapter and Debug Settings Chapter of the TGS32F103xB Reference Manual. In output mode, PD0 and PD1 can only be configured in 50MHz output mode.

- 7. ADC12\_INx (x represents an integer between 0 and 15) appears in the pin name label in the table, indicating that this pin can be ADC1\_INx or ADC2\_INx. For example: ADC12\_IN9 means that this pin can be configured as ADC1\_IN9 or ADC2\_IN9.

- 8. Pin PA0 in the table corresponds to TIM2\_CH1\_ETR in the multiplex function, which means that the function can be configured as TIM2\_TI1 or TIM2\_ETR. Similarly, the name TIM2\_CH1\_ETR of the remapping multiplexing function corresponding to PA15 has the same meaning.

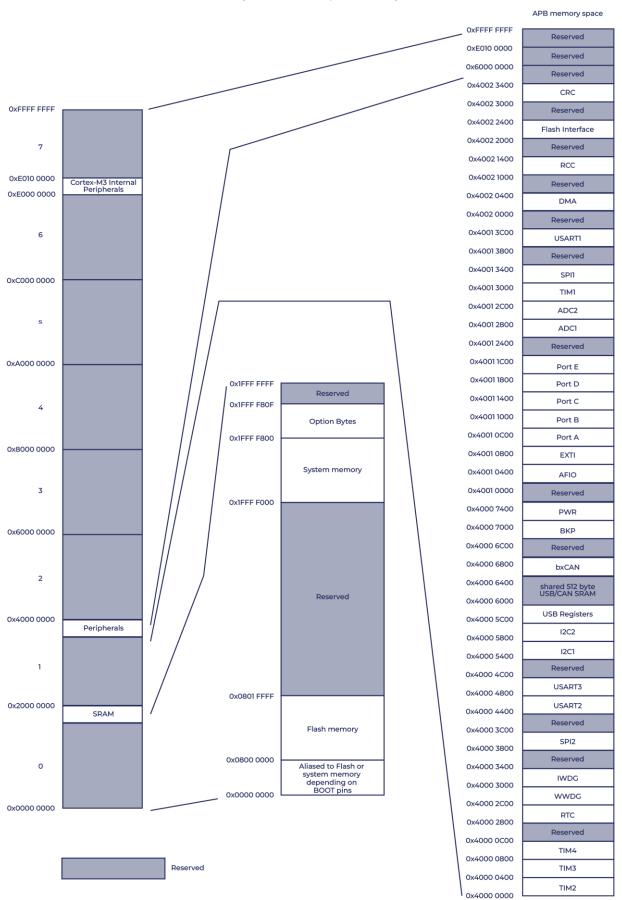

## 4. Memory image

Figure 7. Memory MAP diagram

#### 5. Electrical Characteristics

#### **5.1 Test conditions**

Unless otherwise stated, all voltages are referenced to VSS.

#### 5.1.1 Minimum and maximum values

Unless otherwise stated, all minimum and maximum values will be based on worst-case testing performed on 100% of the product on the production line at an ambient temperature of  $T_A = 25$ °C and  $T_A = T_{Amax}$  ( $T_{Amax}$  matches the selected temperature range). Guaranteed under ambient temperature, supply voltage and clock frequency conditions.

In the notes below each table, it is stated that the data is obtained through comprehensive evaluation, design simulation and/or process characteristics, and will not be tested on the production line; on the basis of comprehensive evaluation, the minimum and maximum values are obtained after passing sample testing. It is obtained by taking the average value and adding or subtracting three times the standard distribution (average  $\pm 3\Sigma$ ).

# 5.1.2 Typical values

Unless otherwise stated, typical data is based on  $T_A = 25^{\circ}\text{C}$  and  $V_{DD} = 3.3 \text{ V}$  ( $2\text{V} \le V_{DD} \le 3.3\text{V}$  voltage range). These data are for design guidance only and have not been tested.

Typical ADC accuracy values are obtained by sampling a standard batch and testing over all temperature ranges. 95% of the products have an error less than or equal to the given value (average  $\pm 2 \Sigma$ ).

## 5.1.3 Typical curve

Unless otherwise stated, typical curves are for design guidance only and have not been tested.

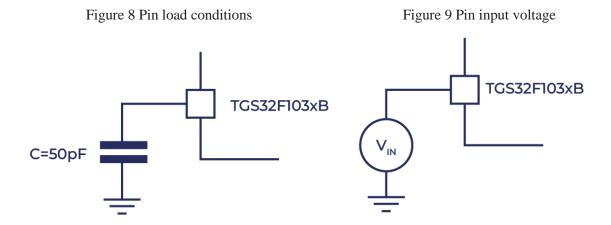

#### **5.1.4** Load capacitance

The load conditions when measuring pin parameters are shown in Figure 8.

#### 5.1.5 Pin input voltage

How the input voltage on the pin is measured is shown in Figure 9.

# **5.1.6** Power supply solution

Backup circuitry Power switch 1.8-3.6V (OSC32K,RTC, Wake-up logic Backup registers) OUT Level shifter 10 GP I/Os Logic IN Kernel logic (CPU, Digital  $V_{DD}$ & Memories) V<sub>DD 1/2/../11</sub> Regulator 11×100nF +1×4.7µF V<sub>SS1/2/../11</sub>  $V_{DD}$  $V_{DDA}$  $V_{REF}$  $\mathsf{v}_{\mathsf{REF}}$ Analog: 10nF 10nF **ADC**  $\mathsf{V}_{\mathsf{REF} ext{-}}$ RCs, PLL +1μΕ +1μΕ  $V_{\underline{SSA}}$

Figure 10. Power supply scheme

Note: The 4.7uf capacitor in the above picture must be connected to  $V_{\text{DD3}}$ .

## **5.1.7** Current consumption measurement

Figure 11. Current consumption measurement scheme

## **5.2 Absolute Maximum Ratings**

Loads applied to the device in excess of those given in the absolute maximum ratings tables (Table 3, Table 4, Table 5) may cause permanent damage to the device. This only gives the maximum load that can be withstood, and does not mean that the functional operation of the device is correct under this condition. Long-term operation of the device under maximum conditions will affect the reliability of the device.

Table 3. Voltage characteristics

| Symbol                            | Describe                                                                        | Minimum<br>value   | Maximum<br>value     | Unit |  |

|-----------------------------------|---------------------------------------------------------------------------------|--------------------|----------------------|------|--|

| V <sub>DD</sub> – V <sub>SS</sub> | External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> | -0.3               | 4.0                  |      |  |

|                                   | Input voltage on 5V tolerant pins <sup>(2)</sup>                                | Vss -0.3           | V <sub>DD</sub> +4.0 | V    |  |

| Vin                               | Input voltage on other pins <sup>(2)</sup>                                      | Vss -0.3           | 4.0                  |      |  |

| $ \Delta V_{\text{DDX}} $         | The voltage difference between different supply pins                            | -                  | 50                   | V    |  |

| Vssx - Vss                        | The voltage difference between different ground pins                            | -                  | 50                   | mV   |  |

| Vesd(hbm)                         | ESD electrostatic discharge voltage (human body model)                          | See Section 5.3.11 |                      |      |  |

<sup>1.</sup> All power  $(V_{DD}, V_{DDA})$  and ground  $(V_{SS}, V_{SSA})$  pins must always be connected to an external power supply system within the allowed range.

Table 4. Current Characteristics

| Symbol                    | Describe                                                                               | Maximum<br>value | Unit |

|---------------------------|----------------------------------------------------------------------------------------|------------------|------|

| $I_{\mathrm{VDD}}$        | Total current through the $V_{DD}/V_{DDA}$ power lines (supply current) <sup>(1)</sup> | 150              |      |

| Ivss                      | Total current through Vss ground (outgoing current)(1)                                 | 150              |      |

| $I_{IO}$                  | Output sink current on any I/O and control pins                                        | 25               |      |

| 110                       | Output current on any I/O and control pins                                             | -25              | mA   |

| I <sub>INJ(PIN)</sub> (2) | 5V Tolerant Pin Injection Current                                                      | -5/+0            |      |

| IINJ(PIN) (=/             | Injection current from other pins <sup>(4)</sup>                                       | ±5               |      |

| $\sum I_{INJ(PIN)}$       | Total injected current on all I/O and control pins <sup>(4)</sup>                      | ±25              |      |

<sup>1.</sup> All power supply  $(V_{DD}, V_{DDA})$  and ground  $(V_{SS}, V_{SSA})$  pins must always be connected to the external power supply system within the allowed range.

- 2.  $I_{INJ(PIN)}$  must not exceed its limit, that is, ensure that  $V_{IN}$  does not exceed its maximum value. If it cannot be guaranteed that  $V_{IN}$  does not exceed its maximum value, it must also be ensured that the external limit  $I_{INJ(PIN)}$  does not exceed its maximum value. When  $V_{IN} > V_{DD}$ , there is a forward injection current; when  $V_{IN} < V_{SS}$ , there is a reverse injection current.

- 3. Reverse injection of current can interfere with the analog performance of the device. See Section 5.3.17.

- 4. When several I/O ports have injection currents at the same time, the maximum value of  $\Sigma$  I<sub>INJ(PIN)</sub> is the sum of the immediate absolute values of the forward injection current and the reverse injection current. This result is based on the characteristics of the maximum value of  $\Sigma$  I<sub>INJ(PIN)</sub> on the device's 4 I/O ports.

Table 5. Temperature characteristics

| Symbol | Describe                     | Numerical value | Unit |

|--------|------------------------------|-----------------|------|

| Tstg   | Storage temperature range    | -65~+150        | °C   |

| Тı     | Maximum junction temperature | 150             | °C   |

<sup>2.</sup>  $I_{INJ(PIN)}$  must not exceed its limit (see Table 4), that is, ensure that  $V_{IN}$  does not exceed its maximum value. If it cannot be guaranteed that  $V_{IN}$  does not exceed its maximum value, it must also be ensured that the external limit  $I_{INJ(PIN)}$  does not exceed its maximum value. When  $V_{IN} > V_{INmax}$ , there is a forward injection current; when  $V_{IN} < V_{SS}$ , there is a reverse injection current.

# **5.3** Working conditions

# **5.3.1** General working conditions

Table 6. General operating conditions

| Symbol             | Parameter                                       |                                               | Condition                       | Minimum value | Maximum value        | Unit |

|--------------------|-------------------------------------------------|-----------------------------------------------|---------------------------------|---------------|----------------------|------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                    |                                               | -                               | 0             | 72                   |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                   |                                               | -                               | 0             | 36                   | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                   |                                               | -                               | 0             | 72                   |      |

| $V_{ m DD}$        | Standard working voltage                        |                                               | -                               | 2             | 3.6                  |      |

| $V_{DDA}^{(1)}$    | Analog section operating voltage (ADC not used) | Must be                                       | the same as $V_{DD}^{(2)}$      | 2             | 3.6                  |      |

|                    | Analog part operating voltage (using ADC)       |                                               |                                 | 2.4           | 3.6                  |      |

| $V_{BAT}$          | Backup part of the working voltage              |                                               | -                               | 1.8           | 3.6                  | V    |

|                    |                                                 | S                                             | Standard I/O                    | -0.3          | V <sub>DD</sub> +0.3 |      |

| $V_{\mathrm{IN}}$  | I/O input valtage                               | /O input voltage $FT I/O = 2V < V_{DD} < 3.0$ |                                 | -0.3          | 5.5                  |      |

| V IN               | 1/O input voltage                               | 111/0                                         | $V_{DD} = 2V$                   | -0.3          | 5.2                  |      |

|                    |                                                 | BOOT0                                         |                                 | 0             | 5.5                  |      |

|                    |                                                 | LQFP100                                       |                                 | -             | 434                  |      |

| $P_{\mathrm{D}}$   | Power dissipation                               |                                               | LQFP64                          | -             | 444                  | mW   |

| ТD                 | Tower dissipation                               |                                               | LQFP48                          | -             | 363                  |      |

|                    |                                                 |                                               | QFN36                           | -             | 1000                 |      |

|                    |                                                 | Maximu                                        | m power dissipation             | -45           | 105                  |      |

| $T_{A}$            | Ambient temperature                             | Low po                                        | ower dissipation <sup>(4)</sup> | -45           | 105                  | °C   |

| $T_{J}$            | Junction temperature range                      | Ten                                           | nperature label                 | -60           | 150                  |      |

<sup>1.</sup> When using the ADC, see Table 43.

<sup>2.</sup> It is recommended to use the same power supply to power  $V_{DD}$  and  $V_{DDA}$ , and a maximum of 300mV difference between  $V_{DD}$  and  $V_{DDA}$  is allowed during power-up and normal operation.

<sup>3.</sup> If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_J$  max (see Section 1).

<sup>4.</sup> Under lower power dissipation conditions,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 1).

# 5.3.2 Operating conditions when powering on and off

The parameters given in the table below are tested under general working conditions.

Table 7. Operating conditions during power-on and power-down

| Symbol           | Parameter                    | Condition | Minimum<br>value | Maximum<br>value | Unit |  |

|------------------|------------------------------|-----------|------------------|------------------|------|--|

| 4                | V <sub>DD</sub> rising rate  |           | 0                | 8                | μs/V |  |

| t <sub>VDD</sub> | V <sub>DD</sub> falling rate | -         | 20               | $\infty$         |      |  |

# **5.3.3** Embedded reset and power control module features

The parameters given in the table below are based on testing at the ambient temperatures and  $V_{\text{DD}}$  supply voltage listed in Table 6.

Table 8. Embedded Reset and Power Control Module Features

| Symbol                              | Parameter                           | Condition                    | Minimum<br>value | Typical<br>value | Maximum value | Unit |

|-------------------------------------|-------------------------------------|------------------------------|------------------|------------------|---------------|------|

|                                     |                                     | PLS[2:0]=000 (rising edge)   | 2.1              | 2.18             | 2.26          | V    |

|                                     |                                     | PLS[2:0]=000 (falling edge)  | 2                | 2.08             | 2.16          | V    |

|                                     |                                     | PLS[2:0]=001 (rising edge)   | 2.19             | 2.28             | 2.37          | V    |

|                                     |                                     | PLS[2:0]=001 (falling edge)  | 2.09             | 2.18             | 2.27          | V    |

|                                     |                                     | PLS[2:0]=010 (rising edge)   | 2.28             | 2.38             | 2.48          | V    |

|                                     |                                     | PLS[2:0]=010 (falling edge)  | 2.18             | 2.28             | 2.38          | V    |

|                                     | D 11                                | PLS[2:0]=011 (rising edge)   | 2.38             | 2.48             | 2.58          | V    |

| 37                                  | Programmable                        | PLS[2:0]=011 (falling edge)  | 2.28             | 2.38             | 2.48          | V    |

| $V_{\mathrm{PVD}}$                  | voltage detector<br>level selection | PLS[2:0]=100 (rising edge)   | 2.47             | 2.58             | 2.69          | V    |

|                                     |                                     | PLS[2:0]=100 (falling edge)  | 2.37             | 2.48             | 2.59          | V    |

|                                     |                                     | PLS[2:0]= 101 (rising edge)  | 2.57             | 2.68             | 2.79          | V    |

|                                     |                                     | PLS[2:0]= 101 (falling edge) | 2.47             | 2.58             | 2.69          | V    |

|                                     |                                     | PLS[2:0]= 110 (rising edge)  | 2.66             | 2.78             | 2.90          | V    |

|                                     |                                     | PLS[2:0]=110 (falling edge)  | 2.56             | 2.68             | 2.80          | V    |

|                                     |                                     | PLS[2:0]=111 (rising edge)   | 2.76             | 2.88             | 3.00          | V    |

|                                     |                                     | PLS[2:0]=111 (falling edge)  | 2.66             | 2.78             | 2.90          | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis                      | -                            | -                | 100              | -             | mV   |

| Vnon man                            | Power-on/power-off                  | falling edge                 | 1 8(1)           | 1.88             | 1.96          | V    |

| V <sub>POR/PDR</sub>                | reset threshold                     | rising edge                  | 1.84             | 1.92             | 2.0           | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PDR hysteresis                      | -                            | -                | 40               | -             | mV   |

| Trsttempo <sup>(2)</sup>            | Reset duration                      | -                            | 1                | 2.5              | 4.5           | ms   |

<sup>1.</sup> Product characteristics are guaranteed by design to the minimum value  $V_{\mbox{\scriptsize POR/PDR}}$ .

$<sup>2. \ \</sup>mbox{Guaranteed}$  by design, not tested in production.

### 5.3.4 Built-in reference voltage

The parameters given in the table below are based on testing at the ambient temperatures and  $V_{DD}$  supply voltage listed in Table 6.

Table 9. Built-in reference voltage

| Symbol                    | Parameter                                                                  | Condition                                                          | Minimum value | Typical<br>value | Maximum value | Unit |

|---------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------|---------------|------------------|---------------|------|

|                           |                                                                            | $-45^{\circ}\text{C} < \text{T}_{\text{A}} < +105^{\circ}\text{C}$ | 1.16          | 1.20             | 1.26          | V    |

| Ts_vrefint <sup>(1)</sup> | When reading the internal reference<br>voltage, the ADC's<br>Sampling time | -                                                                  | -             | 5.1              | (2)<br>17.1   | μs   |

- 1. Product characteristics are guaranteed by design to the minimum value VPOR/PDR.

- 2. Guaranteed by design, not tested in production.

## 5.3.5 Supply current characteristics

Current consumption is a comprehensive indicator of multiple parameters and factors, including operating voltage, ambient temperature, load on I/O pins, product software configuration, operating frequency, I/O pin toggle rate, program memory The location and code executed, etc.

The current consumption measurement method is explained in Figure 11.

All run-mode current consumption measurements given in this section are obtained while executing a simplified set of code.

Dhrystone 2.1 code equivalent results.

#### **Maximum current consumption**

The microcontroller is under the following conditions:

- All I/O pins are in input mode and connected to a quiescent level V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are turned off unless otherwise noted.

- The access time of the flash memory is adjusted to the frequency of  $f_{HCLK}$  (0 wait cycles when  $0\sim24$  MHz, 0 wait cycles when  $24\sim48$  MHz 1 waiting period, 2 waiting periods when exceeding 48MHz).

- Instruction prefetch function is turned on (tip: this parameter must be set before setting the clock and bus frequency division).

- When peripheral is enabled:  $f_{PCLK1} = f_{HCLK/2}$ ,  $f_{PCLK2} = f_{HCLK}$ .

The parameters given in Table 10, Table 11 and Table 12 are based on testing at the ambient temperature and  $V_{\rm DD}$  supply voltage listed in Table 5.

Table 10. Maximum current consumption in run mode, data processing code running from internal flash memory

| Symbol | Parameter             | Condition                                              | £                         | Ma                | $\mathbf{x}^{(1)}$ | Unit |

|--------|-----------------------|--------------------------------------------------------|---------------------------|-------------------|--------------------|------|

| Symbol | r ai ametei           | Condition                                              | $\mathbf{f}_{	ext{HCLK}}$ | $T_A=85^{\circ}C$ | $T_A=105$ °C       | Omt  |

|        |                       |                                                        | 72MHz                     | 21.5              | 26.88              |      |

|        |                       | External clock, enables all peripherals <sup>(2)</sup> | 48MHz                     | 14.3              | 17.88              |      |

|        |                       |                                                        | 32MHz                     | 10.1              | 12.63              |      |

|        |                       |                                                        | 24MHz                     | 8.6               | 10.75              |      |

|        |                       |                                                        | 16MHz                     | 5.5               | 6.88               |      |

| IDD    | Supply current in run |                                                        | 8MHz                      | 3.0               | 12.63<br>10.75     | A    |

| ממו    | mode                  |                                                        | 72MHz                     | 13.4              | 16.75              | mA   |

|        |                       | E                                                      | 48MHz                     | 11.2              | 14.00              |      |

|        |                       | External clock, turn off                               | 32MHz                     | 6.6               | 8.25               |      |

|        |                       | all<br>peripherals <sup>(2)</sup>                      | 24MHz                     | 5.1               | 6.38               | -    |

|        |                       | peripnerals(2)                                         | 16MHz                     | 3.4               | 4.25               |      |

|        |                       |                                                        | 8MHz                      | 2.0               | 2.50               |      |

- 1. Derived from comprehensive evaluation and not tested in production.

- 2. The external clock is 8MHz, and the PLL is enabled when  $f_{HCLK}$ >8MHz.

Table 11. Maximum Current Consumption in Run Mode, Data Processing Code Running from Internal RAM

| Symbol | Parameter             | Condition                                                    | fhclk | Ma                | $X^{(1)}$          | Unit |    |

|--------|-----------------------|--------------------------------------------------------------|-------|-------------------|--------------------|------|----|

| Symbol | r at affictet         | Condition                                                    | IHCLK | $T_A=85^{\circ}C$ | $T_A=105^{\circ}C$ | Omt  |    |

|        |                       | External clock, enables<br>all<br>peripherals <sup>(2)</sup> | 72MHz | 16.9              | 21.13              |      |    |

|        |                       |                                                              | 48MHz | 12.6              | 15.75              |      |    |

|        |                       |                                                              | 32MHz | 8.0               | 10                 |      |    |

|        |                       |                                                              | 24MHz | 6.0               | 7.5                |      |    |

|        |                       |                                                              | 16MHz | 4.2               | 5.25               |      |    |

| Idd    | Supply current in run |                                                              |       | 8MHz              | 2.6                | 3.25 | mA |

| IDD    | mode                  |                                                              | 72MHz | 7.5               | 9.38               | IIIA |    |

|        |                       |                                                              | 48MHz | 5.9               | 7.38               |      |    |

|        |                       | External clock, turn off                                     | 32MHz | 4.0               | 5.00               |      |    |

|        |                       | all                                                          | 24MHz | 3.5               | 4.38               |      |    |

|        |                       | peripherals <sup>(2)</sup>                                   | 16MHz | 2.8               | 3.50               |      |    |

|        |                       |                                                              | 8MHz  | 1.7               | 2.13               |      |    |

- 1. Based on comprehensive evaluation,  $V_{\text{DDmax}}$  is used in production

- 2. The external clock is 8MHz, and the PLL is enabled when  $f_{\mbox{\scriptsize HCLK}}\!\!>\!\!8\mbox{\scriptsize MHz}.$

Table 12. Maximum current consumption in sleep mode, code running in Flash or RAM

| Crowbal  | Donomoton         | Condition                                             | e                         | Ma            | $\mathbf{x}^{(1)}$            | Unit |  |

|----------|-------------------|-------------------------------------------------------|---------------------------|---------------|-------------------------------|------|--|

| Symbol   | Parameter         | Condition                                             | $\mathbf{f}_{	ext{HCLK}}$ | $T_A = 85$ °C | $T_{A}=105^{\circ} \text{ C}$ | Unit |  |

|          |                   | External clock, enable all peripherals <sup>(2)</sup> | 72MHz                     | 17.1          | 21.38                         |      |  |

|          |                   |                                                       | 48MHz                     | 11.2          | 14.00                         |      |  |

|          |                   |                                                       | 32MHz                     | 8.2           | 10.25                         |      |  |

|          |                   |                                                       | 24MHz                     | 6.9           | 8.63                          | mA   |  |

|          |                   | peripherals                                           | 16MHz                     | 4.2           | 5.25<br>3.25                  |      |  |

| т .      | Supply current in |                                                       | 8MHz                      | 2.6           |                               |      |  |

| $I_{DD}$ | sleep mode        |                                                       | 72MHz                     | 6.8           | 6.8 8.50                      |      |  |

|          |                   | F ( 1111)                                             | 48MHz                     | 3.5           | 4.38                          |      |  |

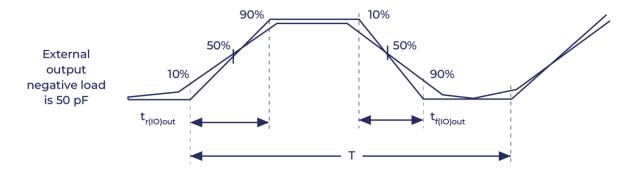

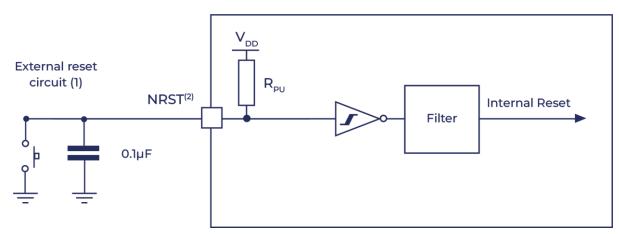

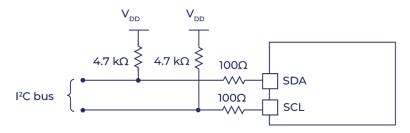

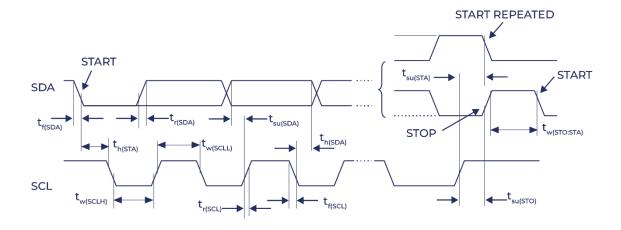

|          |                   | External clock, turn off all                          | 32MHz                     | 3.1           | 3.88                          |      |  |